代写EL1205编程、代做c/c++程序语言

Disclaimer: The information provided in this assessment brief is correct at time of publication. In the unlikely event that any changes

are deemed necessary, they will be communicated clearly via e-mail and a new version of this assessment brief will be circulated.

Academic Year: 2023/24

Assessment Introduction:

Course:

BEng (Hons) Electronic Engineering

Module Code: EL1205

Module Title: Electronic Engineering

Practices

Title of the Brief:

Design & Build: RS232 Character Generator

Type of assessment: Coursework

This Assessment Pack consists of a detailed assignment brief, guidance on what you need to prepare, and

information on how class sessions support your ability to complete successfully. You’ll also find information on this

page to guide you on how, where, and when to submit. If you need additional support, please make a note of the

services detailed in this document.

How, when, and where to submit:

The deadline for this assessment is 12

th April 2024 at 23.59 via the submission zone found the EL1205 Blackboard

area - Please note that this is the final time you can submit – not the time to submit!

If your work is submitted via the Turnitin link on Blackboard, the link will be visible to you on: 8

th March 2024

Feedback will be provided by: 24

th May 2024

You should aim to submit your assessment in advance of the deadline.

Note: If you have any valid mitigating circumstances that mean you cannot meet an assessment submission deadline

and you wish to request an extension, you will need to apply online, via MyUCLan with your evidence prior to the

deadline. Further information on Mitigating Circumstances via this link.

We wish you all success in completing your assessment. Read this guidance carefully, and any questions, please

discuss with your Module Leader or module team.

Additional Support available:

All links are available through the online Student Hub

1. Academic support for this assessment will be provided by contacting Wei Quan

2. Our Library resources link can be found in the library area of the Student Hub or via your subject librarian

at SubjectLibrarians@uclan.ac.uk.

3. Support with your academic skills development (academic writing, critical thinking and referencing) is

available through WISER on the Study Skills section of the Student Hub.

4. For help with Turnitin, see Blackboard and Turnitin Support on the Student Hub

5. If you have a disability, specific learning difficulty, long-term health or mental health condition, and not yet

advised us, or would like to review your support, Inclusive Support can assist with reasonable adjustments

and support. To find out more, you can visit the Inclusive Support page of the Student Hub.

6. For mental health and wellbeing support, please complete our online referral form, or email

wellbeing@uclan.ac.uk. You can also call 01772 893020, attend a drop-in, or visit our UCLan Wellbeing

Service Student Hub pages for more information.

7. For any other support query, please contact Student Support via studentsupport@uclan.ac.uk.

8. For consideration of Academic Integrity, please refer to detailed guidelines in our policy document . All

assessed work should be genuinely your own work, and all resources fully cited.

9. For this assignment, you are not permitted to use any category of AI tools.

Preparing for your assignment.

Ensure that you fully understand the requirements for the assessment and what you are expected to complete. The

assignment will be introduced in the lecture session where you can ask any questions, you can also ask for

clarification by contacting the module team.

The following module learning outcomes will be assessed in this assignment:

• Demonstrate an understanding and application of basic electrical and electronic principles.

• Describe the theory of operation and principal characteristics of simple analogue electronic devices and

circuits.

• Relate the results of experiments on simple analogue electronic circuits to theory.

Please read over the guide to writing a technical document https://www.theiet.org/media/5182/technical-reportwriting.pdf and ensure that you fully understand the requirements of the assessment. There will be a lecture session

on the assignment and writing a technical document.

Ensure that you research and read into the subject area before writing the report so that you have a good

background understanding to the subject area.

Assignment Brief

One of the oldest communications protocol is RS232, or ‘serial’. Up until recently, all PCs had a 9-pin ‘D-type’ serial

port for connecting serial devices like a mouse. RS232 was used on the old ‘teletype’ terminals as a means of

communicating with a host computer. Embedded systems use serial communications to exchange data with other

embedded systems or ‘host’ computers.

An RS232 frame can be composed of a group of 10 bits, clocked out by a 555 timer-based ‘baud rate’ generator. The

bits in this frame can be set low or high by an ‘RDL’ (resistor-diode logic) OR gate. These 5V logic signals can be

converted to the correct RS232 voltage levels by a ‘MAX232’ chip.

A simple RS232 character generator can be made from a 555, a CMOS 4017 decade Johnson Counter (sometimes

called a Ring Counter) and a set of diodes+resistor. A specification for your particular system is given in Appendix A.

You must design and construct a character generator to meet the specification. You must also simulate and measure

its performance and deliver your device and a report for assessment.

In addition to the specification at Appendix A, you should refer to the following documentation:

1. LM555 Timer data sheet. See http://www.national.com/ds/LM/LM555.pdf

2. 4017 data sheet: http://w3.id.tue.nl/fileadmin/id/objects/E-Atelier/doc/Datasheets/40XX/hef4017b.pdf

3. Serial Communication: http://developer.apple.com/documentation/mac/Devices/Devices-313.html

You need to do the following things:

1. Design a circuit to meet the attached specification.

2. Illustrate your circuit design using a schematic diagram created in ISIS.

3. Simulate your circuit design from ISIS using Proteus VSM, to confirm correct operation.

4. Create a PCB layout for your circuit using ARES,

5. Have the PCB made for you by the electronics technicians or create a veroboard layout according to PCB

design.

6. Construct your circuit on PCB/veroboard, using components available from electronics stores.

7. Test your circuit in the laboratory, making appropriate measurements on an oscilloscope and then a PC to

demonstrate that the specification has been met.

8. Document your results in a report, and submit your report and your circuit as described at section 3,

above.

Word limit: A maximum of 1500 words (see notes below for further information).

Technical Report Writing

Your report must have the following contents:

1. A circuit design description including references to source material and incorporating design calculations

where required and a schematic diagram generated from ISIS.

2. Simulation results, generated using Proteus VSM from ISIS, confirming that the design should meet the

specification.

3. A PCB layout for the circuit, generated from ARES.

4. A description of the testing undertaken to show that the circuit meets the specification, matching (within

component value and measurement uncertainties) design calculations and simulation results.

To complete the report, you will have to thoroughly research the area using reliable sources and thoroughly

reference where your information and statements are coming from. The aim of the report is to be clear, concise and

convey technical information to the reader, note that the reader is familiar and experienced in the area. Ensure that

you aim your report for this audience.

A guide on writing a technical document can be found at the following (this will also be uploaded to blackboard):

https://www.theiet.org/media/5182/technical-report-writing.pdf

Please read over the above document to ensure that you are clear on what a technical report is and know what you

are required to complete, note the above is a guide not an explicit standard you will be required to ensure that your

technical report contains the relevant information presented correctly for the reader.

Ensure that you research and read into the subject area before writing the report so that you have a good

background understanding to the subject area. You will need to provide a short report, which shows the calculation

of each tasks in Marking Criteria and Weighting section below with an appropriate assumption, description and

comments, no longer than 1,500 words. You should use the guideline below to structure your report. For the final

reporting submission, make sure that each page is marked with the date of completion, the page number, and the

total number of pages submitted. Make sure that the front page of your submission has this information displayed

prominently along with the module name and number and assignment title. Your work must be referenced using

Harvard Referencing system available here:

https://v3.pebblepad.co.uk/v3portfolio/uclan/Asset/View/Gm3mmGk6sM3RgHZnjGfh7mm6pM.

Further information to support your development will be available to view on assignment briefing session and

Blackboard.

Notes on Wordcount and Referencing

For good marks and given the limited wordcount you should produce work that is: accurate; thorough; well-argued;

clear; accurately referenced; relevant and written in correct (UK) English grammar and spelling. You may include

figures and tables with short captions (25 words each) and a list of references without affecting the overall word

count. Remember that you have limited words so ensure that you “stick to the point” and do not get into detail on

superficial elements.

Ensure that you include references when discussing technical facts and statements on the technology used. You

must reference all your sources of information. These should be cited in the appropriate part of the report and fully

identified to meet the Harvard referencing standard in a list at the end. Website articles must be properly referenced

to be considered as legitimate references.

Presentation of assignment work

Except where specifically stated in the assignment brief, assignment work submissions should be word-processed, in

Microsoft Word 2016 format, with a footer comprising: your module code; date; page number.

The following module learning outcomes will be assessed in this assignment:

• Demonstrate an understanding and application of basic electrical and electronic principles.

• Describe the theory of operation and principal characteristics of simple analogue electronic devices

and circuits.

• Relate the results of experiments on simple analogue electronic circuits to theory

Marking Criteria and Weighting

Your submission will be marked in accordance with the following marking scheme:

Item Weight (%) Model answer criteria

1. Design process and

calculations

10 Concise and accurate calculations and design

decisions, appropriately referenced where

required.

2. ISIS schematic diagram 10 Clear, neat and correctly drawn circuit

schematic.

3. Simulation results 10 Appropriate simulation results, accurately

described and annotated to show important

features.

4. ARES PCB layout 10 Properly laid out PCB, meeting general PCB

requirements as well as specific specification.

5. Test results 20 Accurate description of test procedure and

results, suitably chosen to demonstrate

performance against the specification.

Conclusions on the success or otherwise of

the design.

6. Presentation 10 Presentation requirements met in full.

Concise, complete and well-structured

documentation with correct use of English

throughout. Neat diagrams, clearly presented.

Contents page and page numbers.

7. Hardware 20 Neatly and accurately constructed board, with

good solder joints throughout

8. Demonstration 10 Successfully demonstrate all functionalities of

the hardware implemented

Total 100

Feedback Guidance:

Reflecting on Feedback: how to improve.

From the feedback you receive, you should understand:

• The grade you achieved.

• The best features of your work.

• Areas you may not have fully understood.

• Areas you are doing well but could develop your understanding.

• What you can do to improve in the future - feedforward.

Use the WISER: Academic Skills Development service. WISER can review feedback

and help you understand your feedback. You can also use the WISER Feedback

Glossary

Next Steps:

• List the steps have you taken to respond to previous feedback.

• Summarise your achievements

• Evaluate where you need to improve here (keep handy for future work):

Appendix A - Specification

A.1 General

On the press of a button, the device shall output a stream composed of a single, repeated 7 bit ASCII

character at a given Baud rate to an RS232 interface via a 3.5mm jack plug.

A.2 Construction

The device shall be constructed on a single-sided printed-circuit board (PCB). If additional

connections are required these shall be provided by 0Ω links.

The dimensions of the PCB should be no greater than 60 mm × 60 mm.

10mm clearance should be provided around the pushbutton.

5mm mounting holes should be located at each corner of the board.

A.3 Function

When electrical power is applied the circuit should remain in the reset state. When the pushbutton

is pressed the circuit should deliver a stream composed of a single 7 bit ASCII character at the

specified baud rate (characters and baud rates shown below).

A.3.1 Power supply voltage range

There shall be two electrical connections to the device, to provide electrical power. They shall be

denoted GND (ground) and VS (supply). The supply voltage, measured with respect to ground, will

be +5 V. Power supply connections (VS and GND) shall be by means of a 2-way connection terminal

located at the edge of the board.

A.3.2 Characters and Baud Rates

You are each assigned a combination of Baud Rate and ASCII character – see the table overleaf:

Appendix B – Baud Rate and Character Allocation

Surname First Name Baud Rate ASCII Character

1

AO Bowen 1200 A

2

BAI Hao 2400 B

3

BI Sizhou 4800 C

4

CHEN Siyuan 9600 D

5

CHEN Zihan 14400 E

6

CHEN Haoliang 1200 F

7

CHEN Yanheng 2400 G

8

CHEN Tianyu 4800 H

9

DA Yixuan 9600 I

10 DENG Ruigang 14400 J

11 DIAO Zike 1200 K

12 DONG Mingrui 2400 L

13 FANG Xinyue 4800 M

14 FANG Peijun 9600 N

15 FENG Chuyue 14400 O

16 FU Haoen 1200 P

17 GAO Yuyang 2400 Q

18 GAO Xiaoli 4800 R

19 GAO Jilin 9600 S

20 GE Binkai 14400 T

21 GU Junchao 1200 U

22 GUO Jinhang 2400 V

23 GUO Chaolu 4800 X

24 HOU Jiaqi 9600 Y

25 HU Kaiyu 14400 Z

26 JI Yuxuan 1200 a

27 JIANG Rui 2400 b

28 KE Mengde 4800 c

29 KONG Lingzhe 9600 d

30 LI Tianchen 14400

e

31 LI Jiatong 1200

f

32 LI Mingzi 2400

g

33 LI Chong 4800

h

34 LI Yuxin 9600

i

35 LI Pinge 14400

j

36 LI Yufeng 1200

k

37 LI Xinye 2400

l

38 LIU Hanbing 4800

m

39 LIU Xili 9600

n

40 LIU Duoduo 14400

o

41 LIU Junyu 1200

p

42 LIU Yichen 2400

q

43 LIU Jiayi 4800

r

44 LIU Xuan 9600

s

45 LIU Jinhao 14400

t

46 LU Jiawei 1200

u

47 NIU Chengzhi 2400

v

48 OU Jincheng 4800

w

49 QIANG Yuxuan 9600

x

50 SHEN Jingyi 14400

y

51 SONG Jiayi 1200

z

52 SUN Xitong 2400

1

53 SUN Rui 4800

2

54 TAN Bowen 9600

3

55 WANG Jiaqin 14400

4

56 WANG Jiachen 1200

5

57 WANG Yuhan 2400

6

58 WANG Dacheng 4800

7

59 WANG Qinyi 9600

8

60 WANG Zheng 14400

9

61 WEI Yuchen 1200 NUL

62 WEN Jiayu 2400 SOH

63 WU Changyi 4800 STX

64 XIA Yang 9600 ETX

65 XIAO Tianjian 14400 EOT

66 XIAO Shenjian 1200 ENQ

67 XU Kuanghao 2400 ACK

68 XU Yinchuan 4800 BEL

69 XU Wenle 9600 BS

70 XU Xuanyue 14400 TAB

71 XU Xinyuan 1200 LF

72 XU Zilin 2400 VT

73 XU Jie 4800 FF

74 XUE Wenhao 9600 CR

75 YAN Yuxin 14400 SO

76 YAN Xinyi 1200 SI

77 YANG Hongyu 2400 DLE

78 YANG Haoyu 4800 DC1

79 YANG Jiahao 9600 DC2

80 YANG Jiahao 14400 DC3

81 YU Siyu 1200 DC4

82 YU Wenbo 2400 NAK

83 ZHANG Xiyue 4800 SYN

84 ZHANG Keke 9600 ETB

85 ZHANG Zuping 14400 CAN

86 ZHANG Jingcheng 1200 EM

87 ZHANG Ziran 2400 SUB

88 ZHAO Baiwen 4800 ESC

89 ZHAO Taicheng 9600 FS

90 ZHAO Linye 14400 GS

91 ZHAO Haomiao 1200 RS

92 ZHAO Hanbin 2400

A

93 ZHOU Shuye 4800

B

94 AO Bowen 9600

C

95 BAI Hao 14400

D

96 BI Sizhou 1200

E

Appendix C: Serial Communication

Asynchronous Serial Communication Protocol

Taken from: http://developer.apple.com/documentation/mac/Devices/Devices-313.html

This section provides an overview of the protocol that governs the lowest level of data

transmission--how serialized bits are sent over a single electrical line. This standard rests

on more than a century of evolution in teleprinter technology.

When a sender is connected to a receiver over an electrical connecting line, there is an initial

state in which communication has not yet begun, called the idle or mark state. Because older

electromechanical devices operate more reliably with current continually passing through

them, the mark state employs a positive voltage level. Changing the state of the line by shifting

the voltage to a negative value is called a space. Once this change has occurred, the receiver

interprets a negative voltage level as a 0 bit, and a positive voltage level as a 1 bit. These

transitions are shown in Figure 7-1.

The change from mark to space is known as the start bit, and this triggers the synchronization

necessary for asynchronous serial transmission. The start bit delineates the beginning of the

transmission unit defined as a character frame. The receiver then samples the voltage level at

periodic intervals known as the bit time, to determine whether a 0-bit or a 1-bit is present on

the line.

Figure 7-1 The format of serialized bits

The bit time is expressed in samples per second, known as baud (in honour of

telecommunication pioneer Emile Baudot). This sampling rate must be agreed upon by sender

and receiver prior to start of transmission in order for a successful transfer to occur. Common

values for the sampling rate are 1200 baud and 2400 baud. In the case where one sampling

interval can signal a single bit, a baud rate of 1200 results in a transfer rate of 1200 bits per

second (bps). Note that because modern protocols can express more than one bit value within

the sampling interval, the baud rate and the data rate (bps) are not always identical.

Prior to transmission, the sender and receiver agree on a serial data format; that is, how many

bits of data constitute a character frame, and what happens after those bits are sent. The Serial

Driver supports frames of 5, 6, 7, or 8 bits in length. Character frames of 7 or 8 data bits are

commonly used for transmitting ASCII characters.

LSB MSB

After the data bits in the frame are sent, the sender can optionally transmit a parity bit for errorchecking. There are various parity schemes, which the sender and receiver must agree upon

prior to transmission. In odd parity, a bit is sent so that the entire frame always contains an odd

number of 1 bits. Conversely, in even parity, the parity bit results in an even number of 1 bits.

No parity means that no additional bit is sent. Other less-used parity schemes include mark

parity, in which the extra bit is always 1, and space parity, in which its value is always 0. Using

parity bits for error checking, regardless of the scheme, is now considered a rudimentary

approach to error detection. Most communication systems employ more reliable techniques for

error detection and correction.

To signify the end of the character frame, the sender places the line back to the mark state

(positive voltage) for a minimum specified time interval. This interval has one of several

possible values: 1 bit time, 2 bit times, or 1-1/2 bit times. This signal is known as the stop bit,

and returns the transmission line back to idle status.

Electrical lines are always subject to environmental perturbations known as noise. This noise

can cause errors in transmission, by altering voltage levels so that a bit is reversed (flipped),

shortened (dropped), or lengthened (added). When this occurs, the ability of the receiver to

distinguish a character frame may be affected, resulting in a framing error.

Appendix D: 4017 Johnson Counter

The CMOS 4017 integrated circuit contains 5 flip-flops and 27 logic gates arranged to produce

a Johnson Counter. CMOS is a very flexible logic circuit technology which allows a range of

power supply voltages from 5V to 15V; the same CMOS logic technology is used in

microprocessors (although their power supply voltages are reduced to conserve power).

A Johnson Counter takes a clock (pulse) input, and outputs a single pulse on each of its 10

output pins in turn – the timing diagram is given as part of the data sheet below.

Controlling the timer

The Function table shown below indicates that a rising input on CP0 or a falling input on CP1

causes the counter to advance. The device can be reset using a high (logic 1) on the Master

Reset (MR) input; this rests the 4017 so that it outputs a 1 on the first output pin (O0).

请加QQ:99515681 邮箱:99515681@qq.com WX:codinghelp

- 国际市场 我有WhatsApp拉群营销工具 我无所畏惧

- 业界创新之选 海外行销专家一致认可WhatsApp拉群工具的业务助力

- instagram一键自动采集博主粉丝,ins外贸营销推广软件

- ins营销推广新招!Ins博主推荐群发打粉软件,Instagram利器分享!

- 掌上汽车:引领智能出行新风尚

- 首届全国生物表型标准化工作组成立 神州医疗助力生物医学研究高质量发展

- Ins群发工具震撼发布,Instagram营销软件助你快速引流!

- 精准管理网络通信:Line协议号注册器助力工程师轻松分配标识

- Telegram协议号管理:有效提升网络通信效率!

- 创意风暴来袭 WhatsApp拉群营销工具助你的消息在市场中独领创意风骚 成为行业翘楚

- WhatsApp营销软件,ws群发/ws频道号/ws协议号/ws拉群/ws业务咨询大轩

- 中囤律商信用管理有限公司:引领企业信用修复与ISO体系认证的新篇章

- 市场颠覆者:代筛全球app推广助您领跑竞争

- 专业人士纳闷 WhatsApp拉群营销工具真的是业务成功的关键吗 大家来聊聊

- ins协议私信新玩法!Instagram引流新方式,Ins一键消息发送助你轻松推广!

- Instagram营销群发软件,Ins一键群发工具,助你实现快速推广!

- 2024金智维大模型应用暨新品发布会成功举办,助推新质生产力发展

- 家居建材网:打造您的理想家居,一站式购物新体验

- Instagram热门营销软件,ins群发私信助手/ig营销工具/联系大轩测试

- WhatsApp拉群营销新法宝 有人已经get到了吗 一起来聊聊使用心得

- Ins高效筛选助手,Instagram群发代发工具,让你的营销更高效!

- 2024上海暖通舒适系统展即将开幕,“暖通人”的行业年中盛会!

- Instagram消息群发营销软件,Ins模拟器群发软件,助你快速营销!

- 星际商机的异度航程:WhatsApp筛选器营销在B2B市场的领先策略

- 科技之眼WhatsApp工具 科技魔法师使用的商业预知工具 解码市场趋势的未来密码

- 在国际业务中无往不利 WhatsApp拉群营销工具助你事业海阔天空

- 触手可及的美妙 WhatsApp拉群工具如何打破界限 为用户带来前所未有的感官体验

- 市场智者的选择 WhatsApp工具 专业海外营销专家揭示市场趋势的独到智慧

- 营销新时代,选择 WhatsApp群发协议号轻松推广!让您的品牌消息脱颖而出!

- Telegram快速群发方案,电报采集群发一体机/TG拉群秘籍

推荐

-

苹果罕见大降价,华为的压力给到了?

1、苹果官网罕见大降价冲上热搜。原因是苹

科技

苹果罕见大降价,华为的压力给到了?

1、苹果官网罕见大降价冲上热搜。原因是苹

科技

-

全力打造中国“创业之都”名片,第十届中国创业者大会将在郑州召开

北京创业科创科技中心主办的第十届中国创业

科技

全力打造中国“创业之都”名片,第十届中国创业者大会将在郑州召开

北京创业科创科技中心主办的第十届中国创业

科技

-

智慧驱动 共创未来| 东芝硬盘创新数据存储技术

为期三天的第五届中国(昆明)南亚社会公共安

科技

智慧驱动 共创未来| 东芝硬盘创新数据存储技术

为期三天的第五届中国(昆明)南亚社会公共安

科技

-

如何经营一家好企业,需要具备什么要素特点

我们大多数人刚开始创办一家企业都遇到经营

科技

如何经营一家好企业,需要具备什么要素特点

我们大多数人刚开始创办一家企业都遇到经营

科技

-

创意驱动增长,Adobe护城河够深吗?

Adobe通过其Creative Cloud订阅捆绑包具有

科技

创意驱动增长,Adobe护城河够深吗?

Adobe通过其Creative Cloud订阅捆绑包具有

科技

-

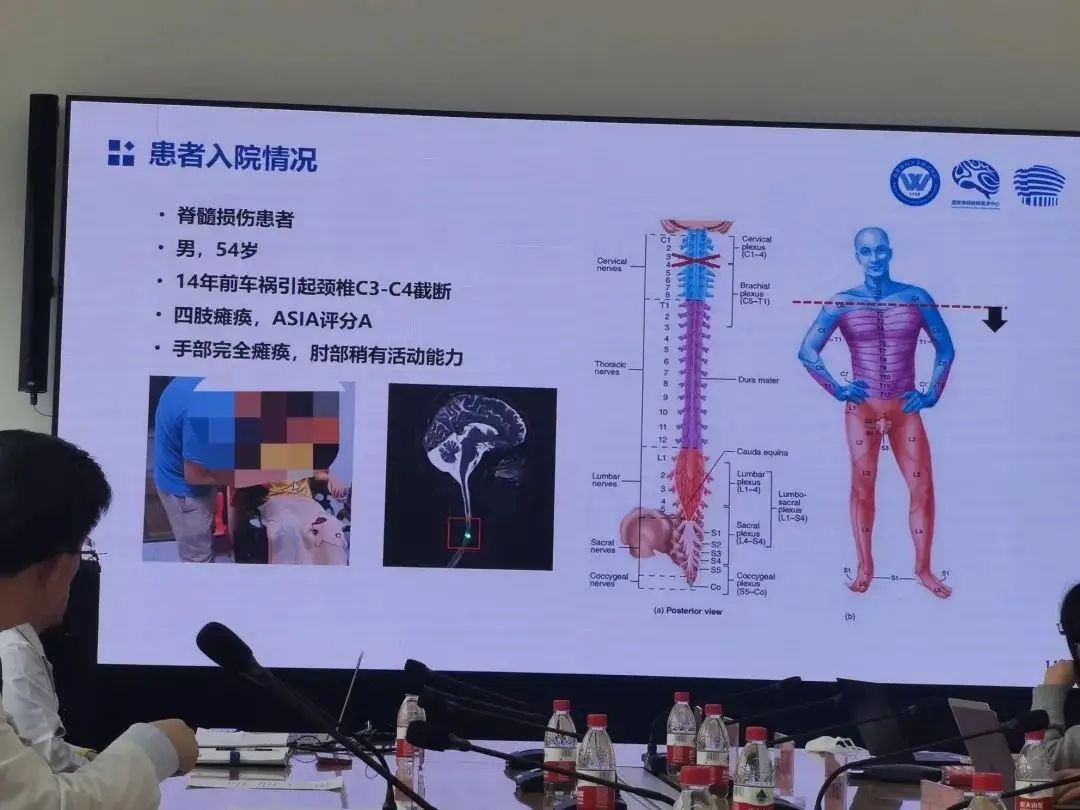

老杨第一次再度抓握住一瓶水,他由此产生了新的憧憬

瘫痪十四年后,老杨第一次再度抓握住一瓶水,他

科技

老杨第一次再度抓握住一瓶水,他由此产生了新的憧憬

瘫痪十四年后,老杨第一次再度抓握住一瓶水,他

科技

-

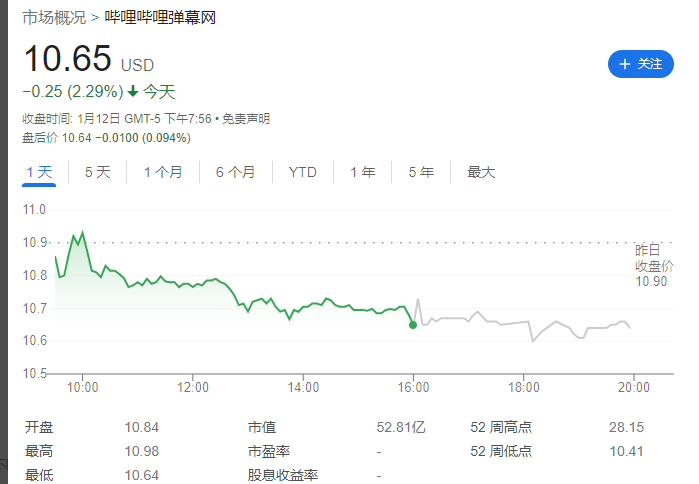

B站更新决策机构名单:共有 29 名掌权管理者,包括陈睿、徐逸、李旎、樊欣等人

1 月 15 日消息,据界面新闻,B站上周发布内部

科技

B站更新决策机构名单:共有 29 名掌权管理者,包括陈睿、徐逸、李旎、樊欣等人

1 月 15 日消息,据界面新闻,B站上周发布内部

科技

-

丰田章男称未来依然需要内燃机 已经启动电动机新项目

尽管电动车在全球范围内持续崛起,但丰田章男

科技

丰田章男称未来依然需要内燃机 已经启动电动机新项目

尽管电动车在全球范围内持续崛起,但丰田章男

科技

-

疫情期间 这个品牌实现了疯狂扩张

记得第一次喝瑞幸,还是2017年底去北京出差的

科技

疫情期间 这个品牌实现了疯狂扩张

记得第一次喝瑞幸,还是2017年底去北京出差的

科技

-

升级的脉脉,正在以招聘业务铺开商业化版图

长久以来,求职信息流不对称、单向的信息传递

科技

升级的脉脉,正在以招聘业务铺开商业化版图

长久以来,求职信息流不对称、单向的信息传递

科技