代做 RV32I single-cycle processor

Tasks

Implement datapath components in RV32I single-cycle processor

2

Control Logic (Decoder)

Tasks

n Implement the Controller

n Impelment the Single-cycle Processor using

p Datapath components implemented in Lab4

– You need to load your Lab4 circ file as a library for using them

p Controller implemented in this Lab

n Test your implementations using

p TestController

p TestRV32I

3

Implement the Controller

n Instructions to support

p Instructions covered in class,

p ECALL instruction

– We use it in a simple way: once the processor encounters an

ECALL instruction, it sets the Halt signal to 1, and the processor

should stop execution (i.e., PC should not be updated any more,

making the processor halts at the ECALL instruction forever)

n You need to implement totally xxx instructions

p See the next slide for more details...

Test Your Controller

n A tester named TestController has been provided to

faciliate your testing of your controller locally

p You can upload and test your implementation on EduCoder

after passing the local test, this will reduce your effort

n The tester is almost done

p Test vectors for the 30 instructions, as well as their

combinations with BrEq/BrLT input signals have been

provided in the corresponding ROMs, and there are 48

elements in each ROM for testing

p But the Result ROM is empty, and you need to fill it with

correct results (each result corresponds to the set of control

signals that should be produced by the controller)

p See the EXCEL file ctr-result.xlsx for more details...

6

Implement the Single-Cycle Processor

n The fetch stage has been given in addition to the input/output pins,

and the IMEM has already been filled with the Fib(6) program (our

processor lacks support for reading a parameter from keyboard)

n You need to implement the rest parts, some important issues include

p How to Halt the processor when encoutering the ECALL instruction?

– Hint: You can use the Halt control signal to disable clock input to PC,

therefore it will not be updated anymore

p The processor should support reading data from an address given by

the input pin Addr, and the data should be passed to the output pin

MData. This will enable us to test that your processor has correctly

executed the program, and the correct result has been writen to the

correct memory location

– Hint: The address input of the DMEM should be able to select from two input

addresses, one from ALU output, and another from the Addr input pin. The

Halt signal can be used to control which path to select

7

Test Your Processor

n The tester (TestRV32I) for your RV32I processor is

simple, but a couple of things to be reminded

p Before testing, you need to set the input pin Addr=0x2000,

because the final result of Fib(6) will be written to this

memory location, and the tester need to read this result from

0x2000

p When the program finished execution (by encountering the

ECALL instruction), the Halt signal becomes 1. Pay attention

to that, and you can check the result of MData to see

whether the it is 0xd (13 in decimal). If yes, your processor

works correctly, and you can upload it to EduCoder for pass

testing.

p The ICount output pin gives the number of instructions that

have been executed, and the PCOut pin gives the address of

currrent instruction

8

List of Files

n RV32I.circ

p The framework of the circuits that you need to implement

n ctr-inst.asm

p The source file containing all instructions and BrEq/BrLT combinations for testing your

controller

n ctr-inst.hex

p The binary of ctr-inst.asm (in textual hex) that has been loaded into the Inst ROM in

TestController

n ctr-breq.hex, ctr-brlt.hex

p The combinations of BrEq/BrLT that are used as input for testing your Controller, which have

been loaded into the BrEq and BrLT ROMs

n ctr-result.xlsx

p The Truth Table for testing your controller. You need to fill it by yourself, and use it to

generate te ctr-result.hex file.

n ctr-result.hex

p The correct result of the generated control signals to compare with the control signals

generated by your controller. You need to load it into the Result_S ROM.

n fib.asm

p The source file of the Fib(6) used for testing your RV32I processor

n fib.hex

p The executable (in textual hex) of Fib(6) that has been loaded into the IMEM

9

The End

请加QQ:99515681 邮箱:99515681@qq.com WX:codinghelp

- 电报最佳群发工具推荐,Telegram全能群发助手,TG拉群发策略

- 光大永明人寿资负联动 做好普惠金融大文章

- Ins快速引粉营销方法,Ig引流工具推荐,instagram群发软件

- 神州医疗弓孟春:基于多模态大数据的生成式AI为临床科研提供新质生产力

- 东北夫妻千里来京做近视手术,爱尔英智眼科周继红:定不负这份信任

- Curia Receives 2024 CDMO Leadership Award

- 会议电视重塑办公场景,皓丽创新大屏新体验

- WhatsApp群发协议号/ws频道号/ws引流营销工具

- Line协议号注册器市场巅峰:我的LINE营销工具心得,让你事业一飞冲天

- 情感共振 WhatsApp拉群营销工具用心打造每个用户的个性化体验之旅

- Instagram自动登录 - ins群发工具/ig营销助手/ins引流神器/引领潮流

- ins拉群软件营销工具的好奇因素是业务成功的关键

- 代写Simple Transport Protocol (STP) UDP protocol.

- Telegram/TG群发拉群自动化软件,电报/TG精准营销软件,TG/纸飞机全自动注册

- EF重启尼泊尔支教之旅项目

- 2024新风口:本地生活直播用虚拟场景“卷”出新红利

- 时空商业的滑稽冒险TG-WS-LINE云控/自动注册机/筛料拉活人:穿越时空,一场科幻时空商业的跨境电商 Line 群发云控笑话之旅即将开始

- 安徽建筑材料:品质卓越,筑梦未来

- COMP30023代写、代做C/C++语言程序

- Instagram群发软件,ins自动登录工具,ig采集工具

- Ins群发脚本助手,Instagram一键群发工具,让你打造营销新格局!

- 在国际舞台 你需要的不仅是勇气 还有一把WhatsApp拉群营销工具的金钥匙

- ADMCF326BRZ: Precision Analog Front-End for Sensory Perfection | ChipsX

- 代做COMP27112、代写C/C++程序语言

- instagramtagram引流利器,智能群发采集,助你实现社交爆发!

- 胡蜂养殖场:探秘自然之韵,品味甜蜜人生

- WhatsApp营销软件,ws拉群/ws代拉/ws代发/ws协议号/ws业务咨询大轩

- 星际商海的新星探:2024年是否有跨境电商 Telegram 群发云控冒险者成为星际商海的新星探,勘探新商机

- Instagram批量群发养号,ins营销引流必备工具/ig采集粉丝神器

- D-Day 杭州站 基于量化高频数据的极速投研实践

推荐

-

升级的脉脉,正在以招聘业务铺开商业化版图

长久以来,求职信息流不对称、单向的信息传递

科技

升级的脉脉,正在以招聘业务铺开商业化版图

长久以来,求职信息流不对称、单向的信息传递

科技

-

全力打造中国“创业之都”名片,第十届中国创业者大会将在郑州召开

北京创业科创科技中心主办的第十届中国创业

科技

全力打造中国“创业之都”名片,第十届中国创业者大会将在郑州召开

北京创业科创科技中心主办的第十届中国创业

科技

-

丰田章男称未来依然需要内燃机 已经启动电动机新项目

尽管电动车在全球范围内持续崛起,但丰田章男

科技

丰田章男称未来依然需要内燃机 已经启动电动机新项目

尽管电动车在全球范围内持续崛起,但丰田章男

科技

-

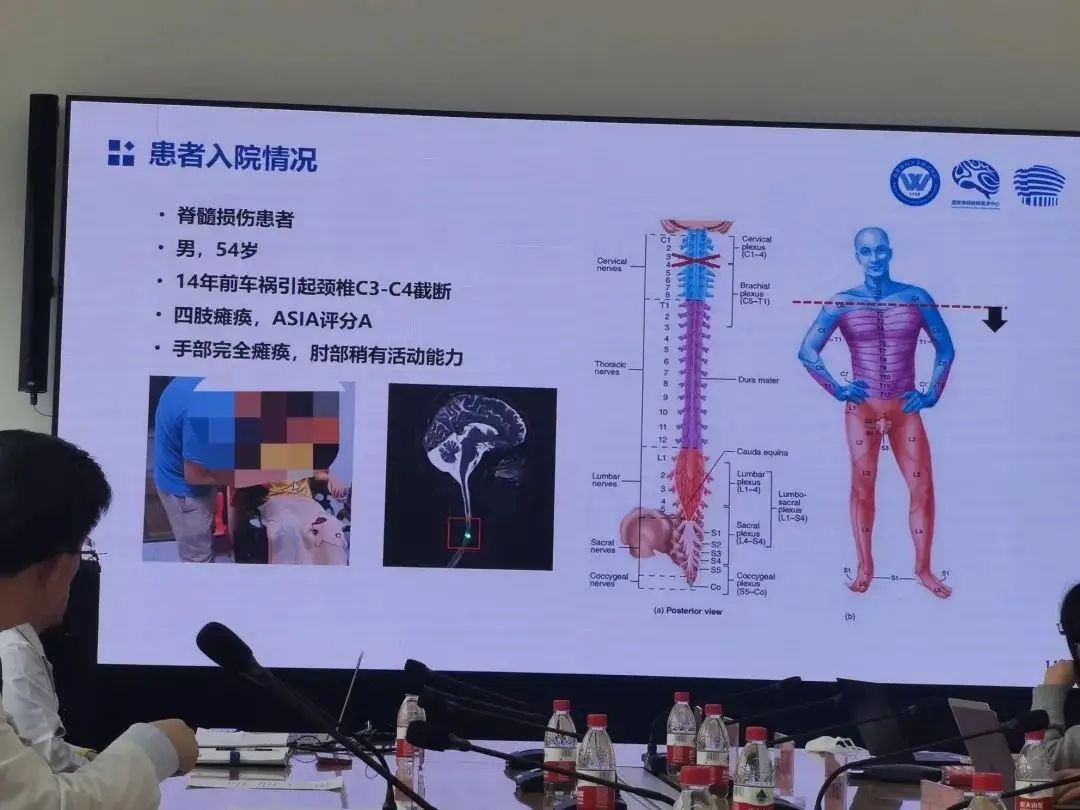

老杨第一次再度抓握住一瓶水,他由此产生了新的憧憬

瘫痪十四年后,老杨第一次再度抓握住一瓶水,他

科技

老杨第一次再度抓握住一瓶水,他由此产生了新的憧憬

瘫痪十四年后,老杨第一次再度抓握住一瓶水,他

科技

-

创意驱动增长,Adobe护城河够深吗?

Adobe通过其Creative Cloud订阅捆绑包具有

科技

创意驱动增长,Adobe护城河够深吗?

Adobe通过其Creative Cloud订阅捆绑包具有

科技

-

苹果罕见大降价,华为的压力给到了?

1、苹果官网罕见大降价冲上热搜。原因是苹

科技

苹果罕见大降价,华为的压力给到了?

1、苹果官网罕见大降价冲上热搜。原因是苹

科技

-

智慧驱动 共创未来| 东芝硬盘创新数据存储技术

为期三天的第五届中国(昆明)南亚社会公共安

科技

智慧驱动 共创未来| 东芝硬盘创新数据存储技术

为期三天的第五届中国(昆明)南亚社会公共安

科技

-

疫情期间 这个品牌实现了疯狂扩张

记得第一次喝瑞幸,还是2017年底去北京出差的

科技

疫情期间 这个品牌实现了疯狂扩张

记得第一次喝瑞幸,还是2017年底去北京出差的

科技

-

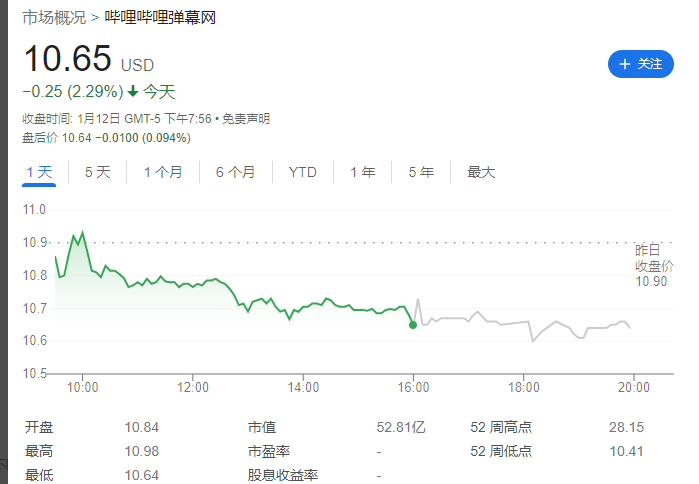

B站更新决策机构名单:共有 29 名掌权管理者,包括陈睿、徐逸、李旎、樊欣等人

1 月 15 日消息,据界面新闻,B站上周发布内部

科技

B站更新决策机构名单:共有 29 名掌权管理者,包括陈睿、徐逸、李旎、樊欣等人

1 月 15 日消息,据界面新闻,B站上周发布内部

科技

-

如何经营一家好企业,需要具备什么要素特点

我们大多数人刚开始创办一家企业都遇到经营

科技

如何经营一家好企业,需要具备什么要素特点

我们大多数人刚开始创办一家企业都遇到经营

科技